- 您现在的位置:买卖IC网 > Sheet目录1998 > ICS844201BG-45LF (IDT, Integrated Device Technology Inc)IC CLK GENERATOR 25MHZ 8TSSOP

ICS844201I-45 Data Sheet

FEMTOCLOCK CRYSTAL-TO-LVDS CLOCK GENERATOR

ICS844201BKI-45 REVISION A OCTOBER 7, 2013

12

2013 Integrated Device Technology, Inc.

Power Considerations

This section provides information on power dissipation and junction temperature for the ICS844201I-45.

Equations and example calculations are also provided.

1.

Power Dissipation.

The total power dissipation for the ICS844201I-45 is the sum of the core power plus the power dissipation in the load(s).

The following is the power dissipation for VDD = 3.3V + 10% = 3.63V, which gives worst case results.

Power (core)MAX = VDD_MAX * IDD_MAX = 3.63V * 95mA = 344.85mW

2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad, and directly affects the reliability of the device. The

maximum recommended junction temperature is 125°C. Limiting the internal transistor junction temperature, Tj, to 125°C ensures that the bond

wire and bond pad temperature remains below 125°C.

The equation for Tj is as follows: Tj =

JA * Pd_total + TA

Tj = Junction Temperature

JA = Junction-to-Ambient Thermal Resistance

Pd_total = Total Device Power Dissipation (example calculation is in section 1 above)

TA = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance

JA must be used. Assuming no air flow and

a multi-layer board, the appropriate value is 74.9°C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

85°C + 0.345W * 74.9°C/W = 110.8°C. This is below the limit of 125°C.

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of

board (multi-layer).

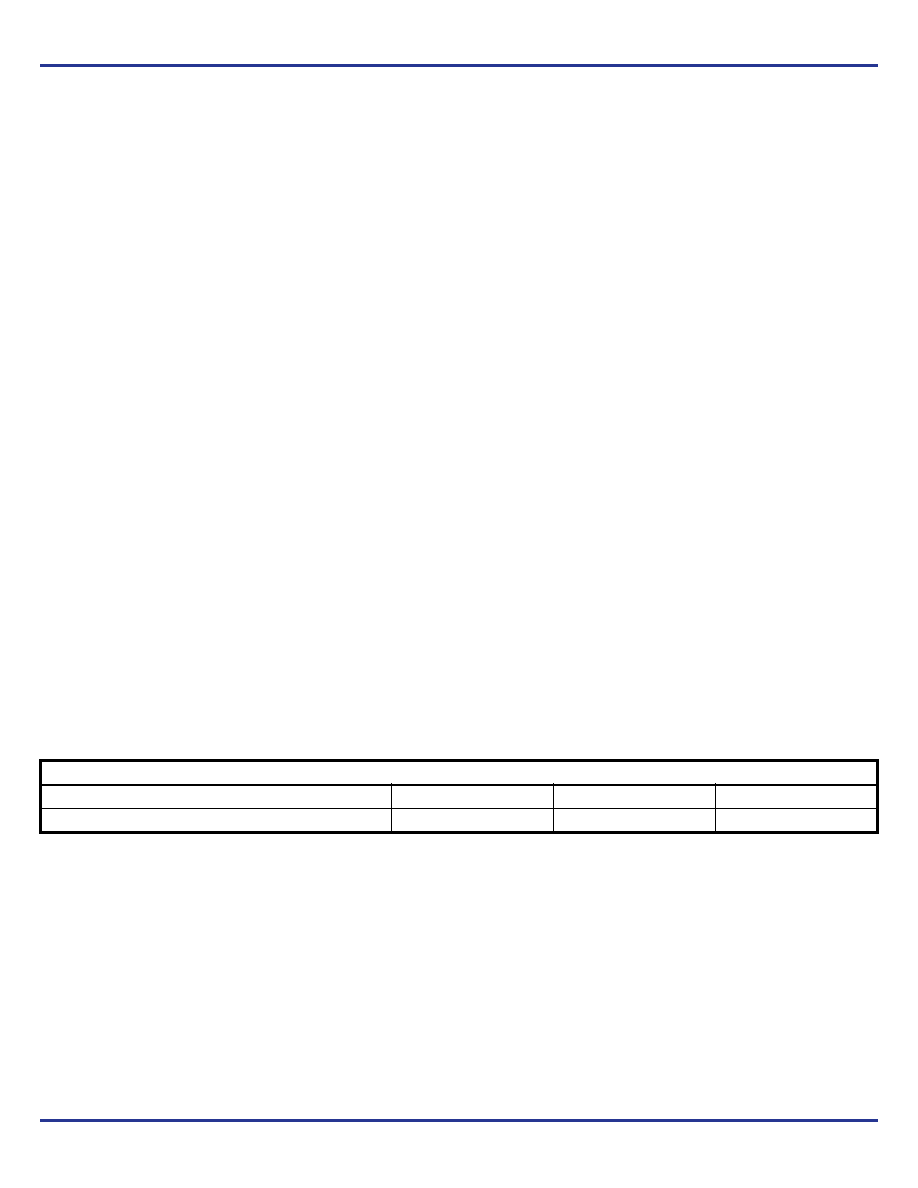

Table 6. Thermal Resistance

JA for 16 Lead VFQFN, Forced Convection

JA vs. Air Flow

Meters per Second

01

2.5

Multi-Layer PCB, JEDEC Standard Test Boards

74.9°C/W

65.5°C/W

58.8°C/W

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS844204BK-245LF

IC CLK SYNTHESIZER 4LVDS 32VFQFN

ICS844S42BKILF

IC SYNTHESIZER RF FREQ 56-VFQFPN

ICS86004BG-01LF

IC CLK BUFFER ZD 1:4 16-TSSOP

ICS8634BY-01LFT

IC BUFFER ZD 1-5 LVPECL 32-LQFP

ICS8701AY-01LF

IC CLK GEN POLARITY CTRL 48-LQFP

ICS8701CYLF

IC CLK GENERATOR /1 /2 48-LQFP

ICS870931ARI-01LF

IC CLK GENERATOR LVCMOS 20QSOP

ICS87158AFLF

IC CLOCK GEN 1-6 HCSL 48-SSOP

相关代理商/技术参数

ICS844201BG-45LFT

功能描述:IC CLK GENERATOR 25MHZ 8TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS844201BGI-45LF

功能描述:IC CLK GENERATOR 25MHZ 8TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS844201BGI-45LFT

功能描述:IC CLK GENERATOR 25MHZ 8TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, FemtoClock™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS844202AK-245LF

功能描述:IC CLOCK GEN SRL SCSI 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS844202AK-245LFT

功能描述:IC CLOCK GEN SRL SCSI 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS844202AKI-245LF

功能描述:IC CLOCK GEN SRL SCSI 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, PCI Express® (PCIe) 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

ICS844202AKI-245LFT

功能描述:IC CLOCK GEN SRL SCSI 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:HiPerClockS™, PCI Express® (PCIe) 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

ICS844204AK-245LF

功能描述:IC CLK SYNTHESIZR 4OUT 32-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:HiPerClockS™ 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT